Streamline

This page documents the new CurrentMakers Streamline series of Green development boards. If you are looking for the previous series, that is document here: STM32World Legacy.

Streamline boards are available here: Streamline on CurrentMakers

Rationale

A number of STM32World Legacy boards have been developed, and produced, and in general the "system" worked very well. It did however have one fatal flaw which was the sole cause of it never being considered for more widespread production. This flaw was the board to board connector.

The original boards used a 2x20 standard pin header on each side giving a result of 80 pins. In terms of connectivity this was a pretty good solution. It did however present some issues:

- Cost - the long pin 2x20 connectors are fairly expensive - around $0.80 each - so $1.60 per board. This may not sound that high but when producing a lot it becomes a serious cost.

- Manufacturing - the headers can not be manufactured with traditional SMD technologies but require a manual step or hand soldering.

- Fragile - when shipping or disconnecting boards it is hard not to bend one or more pins and once bend it becomes extremely difficult to reconnect them.

To get around this flaw a new "connector" was considered and after a long search the best solution was the standard PCI-E X8 connector.

Videos

Receiving the first prototypes ever:

Backplane

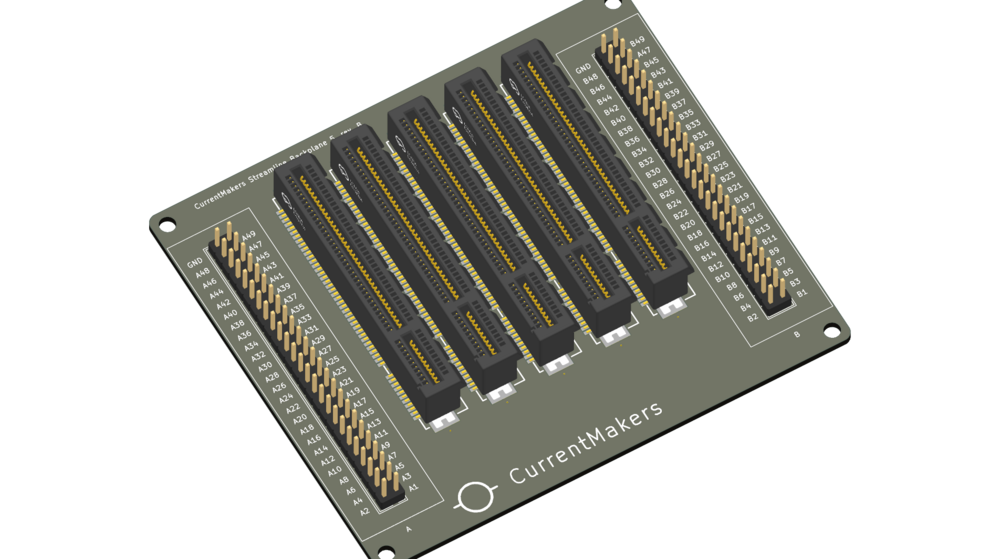

The overall idea is to base StreamLine around a passive backplane. The backplane contains a number of PCI connectors with 2 x 49 pins (98) that is simply connected in a parallel bus.

In each end of the bus all the A and B signals are broken out into regular pin headers.

Backplane rendering

Modules

Backplanes

| Name | Image | Description | Status |

|---|---|---|---|

| Streamline Backplane 5 | Basic 5 position backplane | Available |

Blades

STM32

| Name | Image | Description | Status |

|---|---|---|---|

| Streamline Connect | Streamline Programmer & Debugger. This module is essentially identical to Jolt Connect | Available | |

| Streamline MCU STM32F407 | Streamline MCU board including a STM32F407 | Available | |

| Streamline MCU STM32H562 | Streamline MCU board including a STM32H562 | Available | |

| Streamline MCU STM32L475 | Streamline MCU board including a STM32L475 | Available | |

| Streamline MCU STM32C511 | Streamline MCU board including a STM32C511 | Prototype |

Miscellaneous

| Name | Image | Description | Status |

|---|---|---|---|

| Streamline Neopixel 8x8 | Module with an 8x8 matrix of Neopixel WS2812 LEDs | Available | |

| Streamline Storage SD | Module with Micro-SD slot | Available | |

| Streamline Storage Flash | Module with 16 MB Flash storage (W25q128) | Available | |

| Streamline Storage EEPROM | Module with 512kB EEPROM storage (M24M01) | Available | |

| Streamline Real Time Clock | Real time clock with on board coin cell battery (or supercap) backup | Idea | |

| Streamline ESC | Electronic speed control for BLDC motors | Idea | |

| Streamline HS USB | HS USB blade using USB3300 | Idea | |

| Streamline CAN-FD | CAN-FD bus interface | Idea | |

| Streamline Ethernet | Ethernet interface for STM32F407 | Prototype | |

| Streamline RS485 | Non-isolated RS485 interface | Prototype | |

| Streamline WiFi | WiFi interface | Idea |

Standard Pinout

The pinout table is based on a MCU board with a 100 pin STM32F407. Boards using STM32 MCUs with less pins will leave some of the pins unused.

| STM32 Alt | STM32 | Pin | Pin | STM32 | STM32 Alt |

|---|---|---|---|---|---|

| GND | A1 | B1 | GND | ||

| NRST | A2 | B2 | Boot0 | ||

| VBAT | A3 | B3 | VA | ||

| TIM2_CH3 / TIM5_CH3 / TIM9_CH1 / USART2_TX | PA2 | A4 | B4 | PA3 | TIM2_CH4 / TIM5_CH4 / TIM9_CH2 / USART2_RX / UART4_RX |

| TIM2_CH2 / TIM5_CH2 / UART4_RX / ETH_MII_RX_CLK / ETH_RMII_REF_CLK | PA1 | A5 | B5 | PA4 | SPI1_NSS / I2S3_WS / USART2_CK / DAC1_OUT1 / ETH_MII_CRS |

| TIM2_CH1 / TIM5_CH1 / TIM8_ETR / USART2_CTS / UART4_TX | PA0 | A6 | B6 | PA5 | TIM2_CH1 / TIM8_CH1N / SPI1_SCK / ETH_MII_TX_EN / ETH_RMII_TX_EN |

| TIM8_ETR / SPI2_MOSI / I2S2_MCK / OTG_HS_ULPI_NXT | PC3 | A7 | B7 | PA6 | TIM1_BKIN / TIM3_CH1 / TIM8_BKIN / SPI1_MISO / DCMI_D0 |

| SPI2_MISO / I2S2_ext_SD / DCMI_D8 / ETH_MII_TXD2 / ETH_RMII_TXD1 | PC2 | A8 | B8 | PA7 | TIM1_CH1N / TIM3_CH2 / TIM8_CH1N / SPI1_MOSI / ETH_MII_TX_CLK |

| ETH_MII_MDC / I2S2_SD / SPI2_SD / DCMI_D1 / EVENTOUT | PC1 | A9 | B9 | PC4 | ETH_MII_RXD0 / ETH_RMII_RXD0 / OTG_HS_ULPI_STP / DCMI_D4 |

| OTG_HS_ULPI_STP / DCMI_D1 / EVENTOUT | PC0 | A10 | B10 | PC5 | ETH_MII_RXD1 / ETH_RMII_RXD1 / DCMI_D11 |

| OSC32_OUT | PC15 | A11 | B11 | PB0 | TIM1_CH2N / TIM3_CH3 / TIM8_CH2N / EVENTOUT / DCMI_D2 |

| OSC32_IN | PC14 | A12 | B12 | PB1 | TIM1_CH3N / TIM3_CH4 / TIM8_CH3N / DCMI_D3 |

| PC13 | A13 | B13 | PB2 | ||

| TIM1_BKIN / TIM1_ETR / DCMI_D7 / ETH_MII_TXD3 | PE6 | A14 | B14 | PE7 | TIM1_ETR / UART7_RX / FSMC_D4 / ETH_MII_RX_DV / ETH_RMII_CRS_DV |

| TIM9_CH1 / DCMI_D6 / FSMC_A21 | PE5 | A15 | B15 | PE8 | TIM1_CH1N / UART7_TX / FSMC_D5 |

| TIM9_CH2 / DCMI_D4 / FSMC_A20 / ETH_MII_TXD2 / ETH_RMII_TXD1 | PE4 | A16 | B16 | PE9 | TIM1_CH1 / FSMC_D6 / DCMI_D0 |

| TIM9_CH1 / FSMC_A19 / DCMI_D3 / ETH_MII_TX_CLK / ETH_RMII_REF_CLK | PE3 | A17 | B17 | PE10 | TIM1_CH2N / FSMC_D7 / DCMI_D1 |

| TIM1_CH3N / FSMC_A23 / DCMI_D2 / ETH_MII_TXD3 / ETH_RMII_TXD1 | PE2 | A18 | B18 | PE11 | TIM1_CH2 / FSMC_D8 / DCMI_D2 |

| U1 | A19 | B19 | U2 | ||

| TIM4_ETR / UART8_RX / DCMI_D2 / CAN2_RX / ETH_MII_RX_DV / ETH_RMII_CRS_DV | PE0 | A20 | B20 | PE12 | TIM1_CH3N / FSMC_D9 / DCMI_D3 |

| TIM4_CH1 / UART8_TX / DCMI_D3 / CAN2_TX / ETH_MII_TX_EN / ETH_RMII_TX_EN | PE1 | A21 | B21 | PE13 | TIM1_CH3 / FSMC_D10 / DCMI_D4 |

| TIM4_CH4 / I2C1_SDA / CAN1_TX / SDIO_D5 / DCMI_D7 | PB9 | A22 | B22 | PE14 | TIM1_CH4 / FSMC_D11 / DCMI_D5 |

| TIM4_CH3 / I2C1_SCL / CAN1_RX / SDIO_D4 / ETH_MII_TXD3 | PB8 | A23 | B23 | PE15 | TIM1_BKIN / FSMC_D12 / DCMI_D6 |

| TIM4_CH2 / I2C1_SDA / FSMC_NL | PB7 | A24 | B24 | PB10 | TIM2_CH3 / SPI2_SCK / I2S2_CK / USART3_TX / I2C2_SCL |

| TIM4_CH1 / I2C1_SCL / CAN2_TX | PB6 | A25 | B25 | PB11 | TIM2_CH4 / USART3_RX / I2C2_SDA / ETH_MII_TX_EN / ETH_RMII_TX_EN |

| TIM3_CH2 / SPI1_MOSI / I2S1_SD / CAN2_RX / ETH_MII_COL / OTG_HS_ULPI_D0 | PB5 | A26 | B26 | PB12 | TIM2_ETR / SPI2_NSS / I2S2_WS / USART3_CK / CAN2_RX / OTG_HS_ULPI_D1 / ETH_MII_TXD0 |

| U3 | A27 | B27 | U4 | ||

| TIM3_CH1 / SPI1_MISO / I2S3_ext_SD / JTRST | PB4 | A28 | B28 | PB13 | SPI2_SCK / I2S2_CK / USART3_CTS / CAN2_TX / OTG_HS_ULPI_D2 |

| TIM2_ETR / SPI1_SCK / I2S3_CK / SWO / JTD0 | PB3 | A29 | B29 | PB14 | TIM12_CH1 / SPI2_MISO / I2S2_ext_SD / USART3_RTS / OTG_HS_ULPI_D3 |

| USART2_RTS / FSMC_NWAIT | PD7 | A30 | B30 | PB15 | TIM12_CH2 / SPI2_MOSI / I2S2_SD / USART3_CK / OTG_HS_ULPI_D4 |

| USART2_RX / FSMC_NWAIT / SDIO_D3 / EVENTOUT | PD6 | A31 | B31 | PD8 | USART3_TX / FSMC_D13 / ETH_MII_RXD3 |

| USART2_TX / FSMC_NWE | PD5 | A32 | B32 | PD9 | USART3_RX / FSMC_D14 / DCMI_D10 |

| USART2_RTS / FSMC_NOE | PD4 | A33 | B33 | PD10 | USART3_CK / FSMC_D15 / DCMI_D11 |

| USART2_CTS / FSMC_NADV / SDIO_CMD / DCMI_D5 | PD3 | A34 | B34 | PD11 | USART3_CTS / FSMC_A16 |

| TIM3_ETR / UART5_RX / SDIO_CMD / DCMI_D6 | PD2 | A35 | B35 | PD12 | TIM4_CH1 / USART3_RTS / FSMC_A17 |

| FSMC_D3 / CAN1_TX / ETH_MII_TXD0 / ETH_RMII_TXD0 / OTG_HS_ULPI_D3 | PD1 | A36 | B36 | PD13 | TIM4_CH2 / FSMC_A18 / ETH_MII_TXD1 / ETH_RMII_TXD1 |

| FSMC_D2 / CAN1_RX / ETH_MII_RXD0 / ETH_RMII_RXD0 / OTG_HS_ULPI_D1 | PD0 | A37 | B37 | PD14 | TIM4_CH3 / FSMC_D0 |

| U5 | A38 | B38 | U6 | ||

| UART5_TX / SDIO_CK / DCMI_D9 / SPI3_MOSI / I2S3_SD | PC12 | A39 | B39 | PD15 | TIM4_CH4 / FSMC_D1 |

| UART4_RX / SDIO_D3 / DCMI_D4 / SPI3_MISO / I2S3_ext_SD | PC11 | A40 | B40 | PC6 | TIM3_CH1 / USART6_TX / SDIO_D6 / ETH_MII_TXD3 |

| UART4_TX / SDIO_D2 / DCMI_D8 / SPI3_SCK / I2S3_CK | PC10 | A41 | B41 | PC7 | TIM3_CH2 / USART6_RX / SDIO_D7 / ETH_MII_RX_CLK / ETH_RMII_REF_CLK |

| TIM2_CH1 / ETR / SPI1_NSS / I2S3_WS / JTDI / DCMI_D3 | PA15 | A42 | B42 | PC8 | TIM3_CH3 / USART6_CK / SDIO_D5 / DCMI_D7 |

| JTCK / SWCLK | PA14 | A43 | B43 | PC9 | TIM3_CH4 / I2C3_SDA / SDIO_D6 / DCMI_D8 |

| TIM1_CH4 / USART6_TX / CAN1_RX / OTG_FS_DM | PA11 | A44 | B44 | PA8 | MCO1 / TIM1_CH1 / I2C3_SCL / USART1_CK |

| TIM1_ETR / USART6_RX / CAN1_TX / OTG_FS_DP | PA12 | A45 | B45 | PA9 | TIM1_CH2 / I2C3_SMBA / USART1_TX / DCMI_D0 |

| JTMS / SWDIO / OTG_FS_ID / ETH_MII_TXD3 | PA13 | A46 | B46 | PA10 | TIM1_CH3 / USART1_RX / OTG_FS_ID / DCMI_D1 |

| 3V3 | A47 | B47 | 3V3 | ||

| 5V | A48 | B48 | 5V | ||

| GND | A49 | B49 | GND |