Difference between revisions of "Core Coupled Memory (CCMRAM)"

Jump to navigation

Jump to search

m (Lth moved page Core Coupled Memory to Core Coupled Memory (CCMRAM)) |

|||

| Line 1: | Line 1: | ||

| + | [[Category:STM32]][[Category:STM32 Hardware]][[Category:STM32 Documentation]][[Category:STM32 Development]]{{metadesc|STM32 Core Coupled Memory - CCMRAM}} | ||

Some [[STM32]] [[MCU]]s include a feature called [[CCMRAM]] ([[Core Coupled Memory]]), which is separate from the regular SRAM region. | Some [[STM32]] [[MCU]]s include a feature called [[CCMRAM]] ([[Core Coupled Memory]]), which is separate from the regular SRAM region. | ||

Revision as of 02:32, 28 November 2024

Some STM32 MCUs include a feature called CCMRAM (Core Coupled Memory), which is separate from the regular SRAM region.

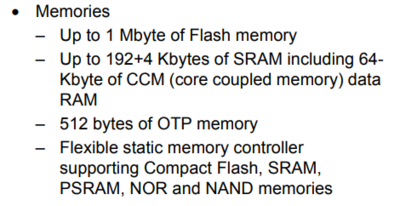

According to the datasheet, the memory in STM32F405 is:

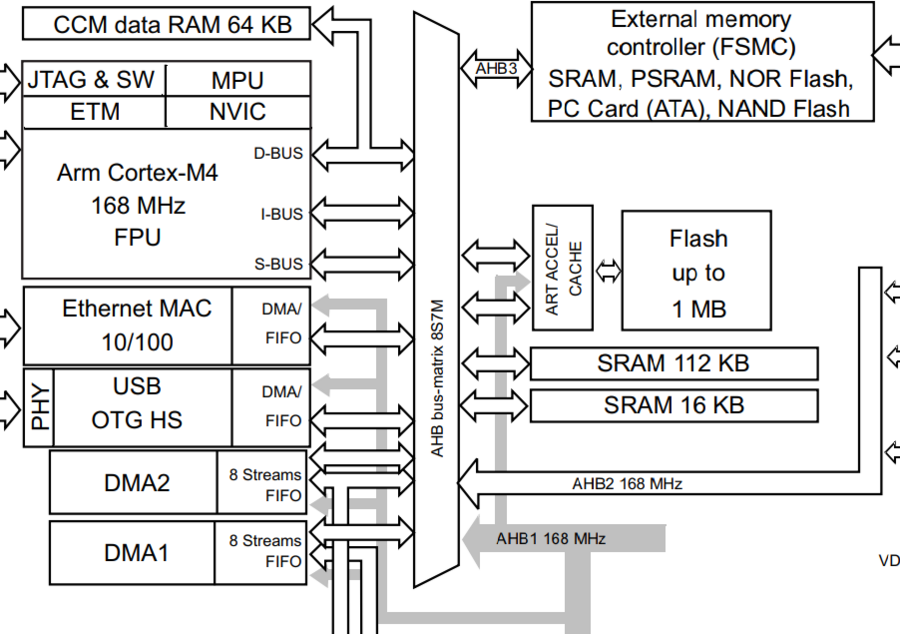

In the block diagram it is shown like this:

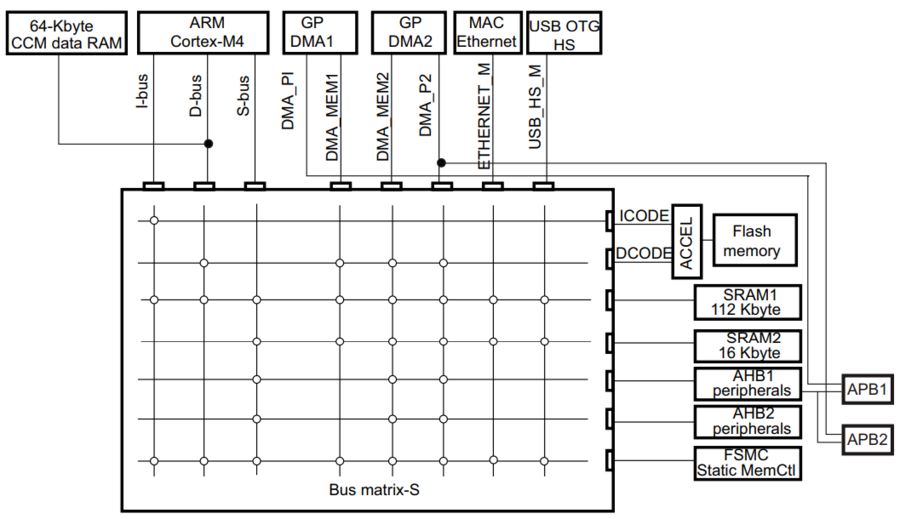

It is worth noticing a few things. As the name implies this RAM is connected directly to the MCU core but separate from the AHB bus matrix. Looking at the bus matrix:

As a result, the CCMRAM can not be used with DMA.