Difference between revisions of "CH32V307V-EVT-R1"

| (4 intermediate revisions by the same user not shown) | |||

| Line 4: | Line 4: | ||

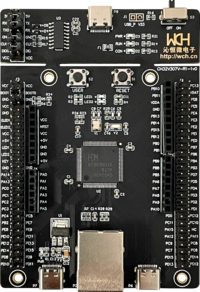

The [[CH32V307V-EVT-R1]] is a [[:Category:Development Board|development board]] for the [[CH32V307]] [[RISC-V]] [[MCU]]. This page contains my initial notes on how to work with this board and the [[CH32V307]] [[MCU]]. My initial experiments are also on Github here: [https://github.com/lbthomsen/CH32V307V-EVT-R1 https://github.com/lbthomsen/CH32V307V-EVT-R1]. | The [[CH32V307V-EVT-R1]] is a [[:Category:Development Board|development board]] for the [[CH32V307]] [[RISC-V]] [[MCU]]. This page contains my initial notes on how to work with this board and the [[CH32V307]] [[MCU]]. My initial experiments are also on Github here: [https://github.com/lbthomsen/CH32V307V-EVT-R1 https://github.com/lbthomsen/CH32V307V-EVT-R1]. | ||

| − | As a development board, this one is clearly inspired by [[ST]]'s [[Nucleo]] boards as it includes an Arduino header as well as a built-in flash/debug tool (they call it [[WCH-Link]] also inspired by [[ST-Link]]). | + | If you got experience and/or questions in relation to this page, please feel free to post them on our [https://www.facebook.com/groups/stm32world Facebook Group]. |

| + | |||

| + | As a development board, this one is clearly inspired by [[ST]]'s [[STM32_Beginner_-_Getting_started#ST_Nucleo|Nucleo]] boards as it includes an Arduino header as well as a built-in flash/debug tool (they call it [[WCH-Link]] also inspired by [[ST-Link]]). | ||

I never really understood why they (both this one and [[ST]]) choose to include an Arduino header. As far as I know, most - if not all - Arduino boards are running at 5V, which makes them possibly incompatible with the 3.3V used on boards such as this. | I never really understood why they (both this one and [[ST]]) choose to include an Arduino header. As far as I know, most - if not all - Arduino boards are running at 5V, which makes them possibly incompatible with the 3.3V used on boards such as this. | ||

| − | The [[CH32V307V-EVT-R1]] board itself is readily availble from [https://lcsc.com/product-detail/Development-Boards-Kits_WCH-Jiangsu-Qin-Heng-CH32V307V-EVT-R1_C2943980.html LCSC] at around $12 (+ shipping). | + | The [[CH32V307V-EVT-R1]] board itself is readily availble from [https://lcsc.com/product-detail/Development-Boards-Kits_WCH-Jiangsu-Qin-Heng-CH32V307V-EVT-R1_C2943980.html LCSC] at around $12 (+ shipping - and you owe me a couple of freebies for the free advertising LCSC). |

== Hardware Description == | == Hardware Description == | ||

| Line 193: | Line 195: | ||

<pre> | <pre> | ||

| − | 11: | + | 11:25:02:880 >> Current project vendor is WCH, debugger is WCH-Link |

| − | + | ||

| − | + | 11:25:02:880 >> Starting to Open Link in RISC-V APP mode... | |

| − | + | 11:25:02:886 >> Open Link in RISC-V APP mode Success | |

| − | + | ||

| − | + | 11:25:02:886 >> Starting to get link mode... | |

| − | + | 11:25:02:886 >> Link is under APP mode | |

| − | + | ||

| − | riscv | + | 11:25:02:886 >> Starting to compare firmware version... |

| − | + | 11:25:02:886 >> No need to update. Already the latest version. Version is v2.3. | |

| − | + | ||

| − | riscv | + | 11:25:02:886 >> Starting to Close Link... |

| − | + | 11:25:02:886 >> Close Link Success | |

| − | riscv | + | 11:25:02:886 >> Starting to Erase All... |

| − | + | "/home/lth/MounRiver_Studio_Community_Linux_x64_V110/MRS_Community/toolchain/OpenOCD/bin/openocd" -f "/home/lth/MounRiver_Studio_Community_Linux_x64_V110/MRS_Community/toolchain/OpenOCD/bin/wch-riscv.cfg" -c init -c halt -c "flash erase_sector wch_riscv 0 last" -c exit | |

| − | + | Open On-Chip Debugger 0.11.0+dev-02215-gcc0ecfb6d-dirty (2022-03-30-18:53) | |

| − | + | Licensed under GNU GPL v2 | |

| − | + | For bug reports, read | |

| − | riscv | + | http://openocd.org/doc/doxygen/bugs.html |

| − | + | Info : only one transport option; autoselect 'jtag' | |

| − | + | Ready for Remote Connections | |

| − | + | Info : WCH-Link version 2.3 | |

| − | + | Info : wlink_init ok | |

| − | + | Info : This adapter doesn't support configurable speed | |

| − | + | Info : JTAG tap: riscv.cpu tap/device found: 0x00000001 (mfg: 0x000 (<invalid>), part: 0x0000, ver: 0x0) | |

| − | + | Warn : Bypassing JTAG setup events due to errors | |

| − | + | Info : [riscv.cpu.0] datacount=2 progbufsize=8 | |

| − | + | Info : Examined RISC-V core; found 1 harts | |

| − | + | Info : hart 0: XLEN=32, misa=0x40901125 | |

| − | + | [riscv.cpu.0] Target successfully examined. | |

| − | + | Info : starting gdb server for riscv.cpu.0 on 3333 | |

| − | + | Info : Listening on port 3333 for gdb connections | |

| − | + | Info : device id = 0xe339e339 | |

| − | + | Info : flash size = 58169kbytes | |

| − | + | erased sectors 0 through 58168 on flash bank 0 in 0.195708s | |

| − | + | ||

| − | + | ||

| − | + | 11:25:03:512 >> Starting to Download... | |

| − | + | "/home/lth/MounRiver_Studio_Community_Linux_x64_V110/MRS_Community/toolchain/OpenOCD/bin/openocd" -f "/home/lth/MounRiver_Studio_Community_Linux_x64_V110/MRS_Community/toolchain/OpenOCD/bin/wch-riscv.cfg" -c init -c halt -c "program \"/home/lth/src/CH32V307V-EVT-R1/first/obj/first.hex\"" -c exit | |

| − | + | Open On-Chip Debugger 0.11.0+dev-02215-gcc0ecfb6d-dirty (2022-03-30-18:53) | |

| − | + | Licensed under GNU GPL v2 | |

| − | + | For bug reports, read | |

| − | + | http://openocd.org/doc/doxygen/bugs.html | |

| − | + | Info : only one transport option; autoselect 'jtag' | |

| − | + | Ready for Remote Connections | |

| − | + | Info : WCH-Link version 2.3 | |

| − | + | Info : wlink_init ok | |

| − | + | Info : This adapter doesn't support configurable speed | |

| − | + | Info : JTAG tap: riscv.cpu tap/device found: 0x00000001 (mfg: 0x000 (<invalid>), part: 0x0000, ver: 0x0) | |

| − | + | Warn : Bypassing JTAG setup events due to errors | |

| − | + | Info : [riscv.cpu.0] datacount=2 progbufsize=8 | |

| − | + | Info : Examined RISC-V core; found 1 harts | |

| − | + | Info : hart 0: XLEN=32, misa=0x40901125 | |

| − | + | [riscv.cpu.0] Target successfully examined. | |

| − | + | Info : starting gdb server for riscv.cpu.0 on 3333 | |

| − | + | Info : Listening on port 3333 for gdb connections | |

| − | + | Info : JTAG tap: riscv.cpu tap/device found: 0x00000001 (mfg: 0x000 (<invalid>), part: 0x0000, ver: 0x0) | |

| − | + | Warn : Bypassing JTAG setup events due to errors | |

| − | + | ** Programming Started ** | |

| − | + | Info : device id = 0x263e6d6e | |

| − | + | Info : flash size = 256kbytes | |

| − | + | ** Programming Finished ** | |

| − | + | ||

| − | + | 11:25:06:504 >> Starting to Verify... | |

| − | + | "/home/lth/MounRiver_Studio_Community_Linux_x64_V110/MRS_Community/toolchain/OpenOCD/bin/openocd" -f "/home/lth/MounRiver_Studio_Community_Linux_x64_V110/MRS_Community/toolchain/OpenOCD/bin/wch-riscv.cfg" -c init -c halt -c "verify_image \"/home/lth/src/CH32V307V-EVT-R1/first/obj/first.hex\"" -c exit | |

| − | + | Open On-Chip Debugger 0.11.0+dev-02215-gcc0ecfb6d-dirty (2022-03-30-18:53) | |

| − | + | Licensed under GNU GPL v2 | |

| − | + | For bug reports, read | |

| − | + | http://openocd.org/doc/doxygen/bugs.html | |

| − | + | Info : only one transport option; autoselect 'jtag' | |

| − | + | Ready for Remote Connections | |

| − | + | Info : WCH-Link version 2.3 | |

| − | + | Info : wlink_init ok | |

| − | + | Info : This adapter doesn't support configurable speed | |

| − | + | Info : JTAG tap: riscv.cpu tap/device found: 0x00000001 (mfg: 0x000 (<invalid>), part: 0x0000, ver: 0x0) | |

| − | + | Warn : Bypassing JTAG setup events due to errors | |

| − | + | Info : [riscv.cpu.0] datacount=2 progbufsize=8 | |

| − | + | Info : Examined RISC-V core; found 1 harts | |

| − | + | Info : hart 0: XLEN=32, misa=0x40901125 | |

| − | + | [riscv.cpu.0] Target successfully examined. | |

| − | + | Info : starting gdb server for riscv.cpu.0 on 3333 | |

| − | + | Info : Listening on port 3333 for gdb connections | |

| − | + | Info : Verify Success | |

| − | + | ||

| − | + | 11:25:08:306 >> Starting to Reset... | |

| − | + | "/home/lth/MounRiver_Studio_Community_Linux_x64_V110/MRS_Community/toolchain/OpenOCD/bin/openocd" -f "/home/lth/MounRiver_Studio_Community_Linux_x64_V110/MRS_Community/toolchain/OpenOCD/bin/wch-riscv.cfg" -c init -c wlink_reset_resume -c exit | |

| − | + | Open On-Chip Debugger 0.11.0+dev-02215-gcc0ecfb6d-dirty (2022-03-30-18:53) | |

| − | + | Licensed under GNU GPL v2 | |

| − | + | For bug reports, read | |

| − | + | http://openocd.org/doc/doxygen/bugs.html | |

| − | + | Info : only one transport option; autoselect 'jtag' | |

| − | + | Ready for Remote Connections | |

| − | + | Info : WCH-Link version 2.3 | |

| − | + | Info : wlink_init ok | |

| − | + | Info : This adapter doesn't support configurable speed | |

| − | + | Info : JTAG tap: riscv.cpu tap/device found: 0x00000001 (mfg: 0x000 (<invalid>), part: 0x0000, ver: 0x0) | |

| − | + | Warn : Bypassing JTAG setup events due to errors | |

| − | + | Info : [riscv.cpu.0] datacount=2 progbufsize=8 | |

| − | + | Info : Examined RISC-V core; found 1 harts | |

| − | + | Info : hart 0: XLEN=32, misa=0x40901125 | |

| − | + | [riscv.cpu.0] Target successfully examined. | |

| − | + | Info : starting gdb server for riscv.cpu.0 on 3333 | |

| − | + | Info : Listening on port 3333 for gdb connections | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | riscv | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | ------------------------------End ------------------------------ | |

| + | Operation Finished (took 6s.176ms) | ||

</pre> | </pre> | ||

| Line 391: | Line 316: | ||

</pre> | </pre> | ||

| − | Notice that the output will actually be printed twice (not shown above) because the MCU is reset twice. | + | Notice that the output will actually be printed twice (not shown above) because the MCU is reset twice during the flashing process. |

=== Single step debugging === | === Single step debugging === | ||

Latest revision as of 06:01, 29 June 2022

The CH32V307V-EVT-R1 is a development board for the CH32V307 RISC-V MCU. This page contains my initial notes on how to work with this board and the CH32V307 MCU. My initial experiments are also on Github here: https://github.com/lbthomsen/CH32V307V-EVT-R1.

If you got experience and/or questions in relation to this page, please feel free to post them on our Facebook Group.

As a development board, this one is clearly inspired by ST's Nucleo boards as it includes an Arduino header as well as a built-in flash/debug tool (they call it WCH-Link also inspired by ST-Link).

I never really understood why they (both this one and ST) choose to include an Arduino header. As far as I know, most - if not all - Arduino boards are running at 5V, which makes them possibly incompatible with the 3.3V used on boards such as this.

The CH32V307V-EVT-R1 board itself is readily availble from LCSC at around $12 (+ shipping - and you owe me a couple of freebies for the free advertising LCSC).

Hardware Description

It is worth noticing that contrary to various ST development boards, the two user LED's and the user button are by default only wired to the header, not the MCU itself. This means that a jumper lead is necessary to use any of these.

MounRiver Studio

Installing

The MounRiver Studio community edition can be downloaded from http://www.mounriver.com/download (warning, insecure link).

Installing it (on Linux) is really quite simple. Unpack the downloaded archive:

lth@ncpws04:~$ tar xvf Downloads/MounRiver_Studio_Community_Linux_x64_V110.tar.xz

After the archive has been unpacked a few tweaks are necessary. MounRiver provided a script for this:

lth@ncpws04:~$ cd MounRiver_Studio_Community_Linux_x64_V110/beforeinstall/ lth@ncpws04:~/MounRiver_Studio_Community_Linux_x64_V110/beforeinstall$ ./start.sh

And that is about it. You can now run MounRiver Studio like this:

lth@ncpws04:~$ ~/MounRiver_Studio_Community_Linux_x64_V110/MRS_Community/MounRiver\ Studio_Community

Creating first project

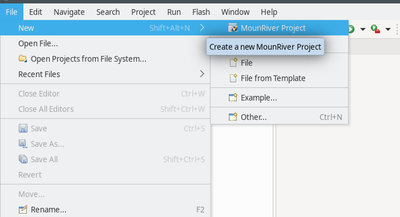

Once the MounRiver Studio has been started, a new project can be created:

In the resulting dialog, first select the appropriate MCU, then give the project a name:

Notice that there is a bug which change the project name once a MCU is selected, so unless you want all your projects to be named after the MCU, do change the name after you select the MCU.

Pressing Ok will generate a source tree, including a main.c in the User directory:

/********************************** (C) COPYRIGHT *******************************

* File Name : main.c

* Author : WCH

* Version : V1.0.0

* Date : 2021/06/06

* Description : Main program body.

* Copyright (c) 2021 Nanjing Qinheng Microelectronics Co., Ltd.

* SPDX-License-Identifier: Apache-2.0

*******************************************************************************/

/*

*@Note

串口打印调试例程:

USART1_Tx(PA9)。

本例程演示使用 USART1(PA9) 作打印调试口输出。

*/

#include "debug.h"

/* Global typedef */

/* Global define */

/* Global Variable */

/*********************************************************************

* @fn main

*

* @brief Main program.

*

* @return none

*/

int main(void)

{

NVIC_PriorityGroupConfig(NVIC_PriorityGroup_2);

Delay_Init();

USART_Printf_Init(115200);

printf("SystemClk:%d\r\n",SystemCoreClock);

printf("This is printf example\r\n");

while(1)

{

}

}

As can be seen, the default application will print out a few statements and then do nothing.

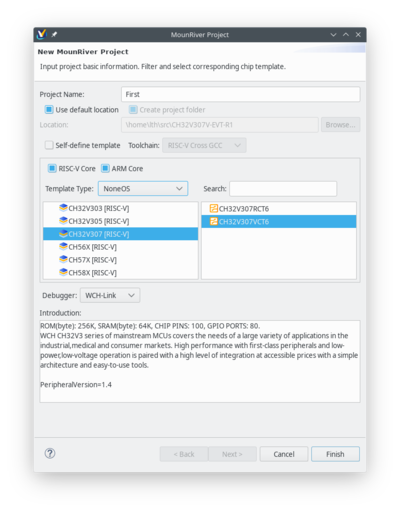

By selecting Project/Build Project

The project should be successfully build. The Console window will show the result of the build process:

11:14:20 **** Build of configuration obj for project first **** make -j4 all Building file: ../User/ch32v30x_it.c Building file: ../User/main.c Building file: ../User/system_ch32v30x.c Invoking: GNU RISC-V Cross C Compiler riscv-none-embed-gcc -march=rv32imac -mabi=ilp32 -msmall-data-limit=8 -mno-save-restore -Os -fmessage-length=0 -fsigned-char -ffunction-sections -fdata-sections -Wunused -Wuninitialized -g -I"/home/lth/src/CH32V307V-EVT-R1/first/Debug" -I"/home/lth/src/CH32V307V-EVT-R1/first/Core" -I"/home/lth/src/CH32V307V-EVT-R1/first/User" -I"/home/lth/src/CH32V307V-EVT-R1/first/Peripheral/inc" -std=gnu99 -MMD -MP -MF"User/ch32v30x_it.d" -MT"User/ch32v30x_it.o" -c -o "User/ch32v30x_it.o" "../User/ch32v30x_it.c" Invoking: GNU RISC-V Cross C Compiler riscv-none-embed-gcc -march=rv32imac -mabi=ilp32 -msmall-data-limit=8 -mno-save-restore -Os -fmessage-length=0 -fsigned-char -ffunction-sections -fdata-sections -Wunused -Wuninitialized -g -I"/home/lth/src/CH32V307V-EVT-R1/first/Debug" -I"/home/lth/src/CH32V307V-EVT-R1/first/Core" -I"/home/lth/src/CH32V307V-EVT-R1/first/User" -I"/home/lth/src/CH32V307V-EVT-R1/first/Peripheral/inc" -std=gnu99 -MMD -MP -MF"User/system_ch32v30x.d" -MT"User/system_ch32v30x.o" -c -o "User/system_ch32v30x.o" "../User/system_ch32v30x.c" Invoking: GNU RISC-V Cross C Compiler Building file: ../Startup/startup_ch32v30x_D8C.S riscv-none-embed-gcc -march=rv32imac -mabi=ilp32 -msmall-data-limit=8 -mno-save-restore -Os -fmessage-length=0 -fsigned-char -ffunction-sections -fdata-sections -Wunused -Wuninitialized -g -I"/home/lth/src/CH32V307V-EVT-R1/first/Debug" -I"/home/lth/src/CH32V307V-EVT-R1/first/Core" -I"/home/lth/src/CH32V307V-EVT-R1/first/User" -I"/home/lth/src/CH32V307V-EVT-R1/first/Peripheral/inc" -std=gnu99 -MMD -MP -MF"User/main.d" -MT"User/main.o" -c -o "User/main.o" "../User/main.c" Invoking: GNU RISC-V Cross Assembler riscv-none-embed-gcc -march=rv32imac -mabi=ilp32 -msmall-data-limit=8 -mno-save-restore -Os -fmessage-length=0 -fsigned-char -ffunction-sections -fdata-sections -Wunused -Wuninitialized -g -x assembler -I"/home/lth/src/CH32V307V-EVT-R1/first/Startup" -MMD -MP -MF"Startup/startup_ch32v30x_D8C.d" -MT"Startup/startup_ch32v30x_D8C.o" -c -o "Startup/startup_ch32v30x_D8C.o" "../Startup/startup_ch32v30x_D8C.S" Finished building: ../Startup/startup_ch32v30x_D8C.S Building file: ../Peripheral/src/ch32v30x_adc.c Invoking: GNU RISC-V Cross C Compiler riscv-none-embed-gcc -march=rv32imac -mabi=ilp32 -msmall-data-limit=8 -mno-save-restore -Os -fmessage-length=0 -fsigned-char -ffunction-sections -fdata-sections -Wunused -Wuninitialized -g -I"/home/lth/src/CH32V307V-EVT-R1/first/Debug" -I"/home/lth/src/CH32V307V-EVT-R1/first/Core" -I"/home/lth/src/CH32V307V-EVT-R1/first/User" -I"/home/lth/src/CH32V307V-EVT-R1/first/Peripheral/inc" -std=gnu99 -MMD -MP -MF"Peripheral/src/ch32v30x_adc.d" -MT"Peripheral/src/ch32v30x_adc.o" -c -o "Peripheral/src/ch32v30x_adc.o" "../Peripheral/src/ch32v30x_adc.c" Finished building: ../User/main.c (!!!repetitive stuff removed here!!!) Invoking: GNU RISC-V Cross C Compiler riscv-none-embed-gcc -march=rv32imac -mabi=ilp32 -msmall-data-limit=8 -mno-save-restore -Os -fmessage-length=0 -fsigned-char -ffunction-sections -fdata-sections -Wunused -Wuninitialized -g -I"/home/lth/src/CH32V307V-EVT-R1/first/Debug" -I"/home/lth/src/CH32V307V-EVT-R1/first/Core" -I"/home/lth/src/CH32V307V-EVT-R1/first/User" -I"/home/lth/src/CH32V307V-EVT-R1/first/Peripheral/inc" -std=gnu99 -MMD -MP -MF"Peripheral/src/ch32v30x_usart.d" -MT"Peripheral/src/ch32v30x_usart.o" -c -o "Peripheral/src/ch32v30x_usart.o" "../Peripheral/src/ch32v30x_usart.c" Building file: ../Peripheral/src/ch32v30x_wwdg.c Invoking: GNU RISC-V Cross C Compiler riscv-none-embed-gcc -march=rv32imac -mabi=ilp32 -msmall-data-limit=8 -mno-save-restore -Os -fmessage-length=0 -fsigned-char -ffunction-sections -fdata-sections -Wunused -Wuninitialized -g -I"/home/lth/src/CH32V307V-EVT-R1/first/Debug" -I"/home/lth/src/CH32V307V-EVT-R1/first/Core" -I"/home/lth/src/CH32V307V-EVT-R1/first/User" -I"/home/lth/src/CH32V307V-EVT-R1/first/Peripheral/inc" -std=gnu99 -MMD -MP -MF"Peripheral/src/ch32v30x_wwdg.d" -MT"Peripheral/src/ch32v30x_wwdg.o" -c -o "Peripheral/src/ch32v30x_wwdg.o" "../Peripheral/src/ch32v30x_wwdg.c" Finished building: ../Peripheral/src/ch32v30x_rcc.c Building file: ../Debug/debug.c Invoking: GNU RISC-V Cross C Compiler riscv-none-embed-gcc -march=rv32imac -mabi=ilp32 -msmall-data-limit=8 -mno-save-restore -Os -fmessage-length=0 -fsigned-char -ffunction-sections -fdata-sections -Wunused -Wuninitialized -g -I"/home/lth/src/CH32V307V-EVT-R1/first/Debug" -I"/home/lth/src/CH32V307V-EVT-R1/first/Core" -I"/home/lth/src/CH32V307V-EVT-R1/first/User" -I"/home/lth/src/CH32V307V-EVT-R1/first/Peripheral/inc" -std=gnu99 -MMD -MP -MF"Debug/debug.d" -MT"Debug/debug.o" -c -o "Debug/debug.o" "../Debug/debug.c" Finished building: ../Peripheral/src/ch32v30x_wwdg.c Building file: ../Core/core_riscv.c Invoking: GNU RISC-V Cross C Compiler riscv-none-embed-gcc -march=rv32imac -mabi=ilp32 -msmall-data-limit=8 -mno-save-restore -Os -fmessage-length=0 -fsigned-char -ffunction-sections -fdata-sections -Wunused -Wuninitialized -g -I"/home/lth/src/CH32V307V-EVT-R1/first/Debug" -I"/home/lth/src/CH32V307V-EVT-R1/first/Core" -I"/home/lth/src/CH32V307V-EVT-R1/first/User" -I"/home/lth/src/CH32V307V-EVT-R1/first/Peripheral/inc" -std=gnu99 -MMD -MP -MF"Core/core_riscv.d" -MT"Core/core_riscv.o" -c -o "Core/core_riscv.o" "../Core/core_riscv.c" Finished building: ../Debug/debug.c Finished building: ../Core/core_riscv.c Finished building: ../Peripheral/src/ch32v30x_usart.c Finished building: ../Peripheral/src/ch32v30x_tim.c Building target: first.elf Invoking: GNU RISC-V Cross C Linker riscv-none-embed-gcc -march=rv32imac -mabi=ilp32 -msmall-data-limit=8 -mno-save-restore -Os -fmessage-length=0 -fsigned-char -ffunction-sections -fdata-sections -Wunused -Wuninitialized -g -T "/home/lth/src/CH32V307V-EVT-R1/first/Ld/Link.ld" -nostartfiles -Xlinker --gc-sections -Wl,-Map,"first.map" --specs=nano.specs --specs=nosys.specs -o "first.elf" ./User/ch32v30x_it.o ./User/main.o ./User/system_ch32v30x.o ./Startup/startup_ch32v30x_D8C.o ./Peripheral/src/ch32v30x_adc.o ./Peripheral/src/ch32v30x_bkp.o ./Peripheral/src/ch32v30x_can.o ./Peripheral/src/ch32v30x_crc.o ./Peripheral/src/ch32v30x_dac.o ./Peripheral/src/ch32v30x_dbgmcu.o ./Peripheral/src/ch32v30x_dma.o ./Peripheral/src/ch32v30x_dvp.o ./Peripheral/src/ch32v30x_eth.o ./Peripheral/src/ch32v30x_exti.o ./Peripheral/src/ch32v30x_flash.o ./Peripheral/src/ch32v30x_fsmc.o ./Peripheral/src/ch32v30x_gpio.o ./Peripheral/src/ch32v30x_i2c.o ./Peripheral/src/ch32v30x_iwdg.o ./Peripheral/src/ch32v30x_misc.o ./Peripheral/src/ch32v30x_opa.o ./Peripheral/src/ch32v30x_pwr.o ./Peripheral/src/ch32v30x_rcc.o ./Peripheral/src/ch32v30x_rng.o ./Peripheral/src/ch32v30x_rtc.o ./Peripheral/src/ch32v30x_sdio.o ./Peripheral/src/ch32v30x_spi.o ./Peripheral/src/ch32v30x_tim.o ./Peripheral/src/ch32v30x_usart.o ./Peripheral/src/ch32v30x_wwdg.o ./Debug/debug.o ./Core/core_riscv.o Finished building target: first.elf Invoking: GNU RISC-V Cross Create Flash Image riscv-none-embed-objcopy -O ihex "first.elf" "first.hex" Invoking: GNU RISC-V Cross Create Listing riscv-none-embed-objdump --all-headers --demangle --disassemble "first.elf" > "first.lst" Invoking: GNU RISC-V Cross Print Size riscv-none-embed-size --format=berkeley "first.elf" text data bss dec hex filename 7160 136 2068 9364 2494 first.elf Finished building: first.hex Finished building: first.siz Finished building: first.lst 11:14:22 Build Finished. 0 errors, 0 warnings. (took 1s.882ms)

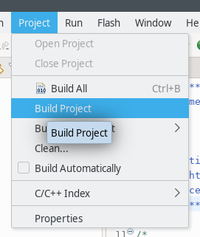

Flashing

Flashing first time should be straight forward. Click on the flash button:

Results in the following console output:

11:25:02:880 >> Current project vendor is WCH, debugger is WCH-Link 11:25:02:880 >> Starting to Open Link in RISC-V APP mode... 11:25:02:886 >> Open Link in RISC-V APP mode Success 11:25:02:886 >> Starting to get link mode... 11:25:02:886 >> Link is under APP mode 11:25:02:886 >> Starting to compare firmware version... 11:25:02:886 >> No need to update. Already the latest version. Version is v2.3. 11:25:02:886 >> Starting to Close Link... 11:25:02:886 >> Close Link Success 11:25:02:886 >> Starting to Erase All... "/home/lth/MounRiver_Studio_Community_Linux_x64_V110/MRS_Community/toolchain/OpenOCD/bin/openocd" -f "/home/lth/MounRiver_Studio_Community_Linux_x64_V110/MRS_Community/toolchain/OpenOCD/bin/wch-riscv.cfg" -c init -c halt -c "flash erase_sector wch_riscv 0 last" -c exit Open On-Chip Debugger 0.11.0+dev-02215-gcc0ecfb6d-dirty (2022-03-30-18:53) Licensed under GNU GPL v2 For bug reports, read http://openocd.org/doc/doxygen/bugs.html Info : only one transport option; autoselect 'jtag' Ready for Remote Connections Info : WCH-Link version 2.3 Info : wlink_init ok Info : This adapter doesn't support configurable speed Info : JTAG tap: riscv.cpu tap/device found: 0x00000001 (mfg: 0x000 (<invalid>), part: 0x0000, ver: 0x0) Warn : Bypassing JTAG setup events due to errors Info : [riscv.cpu.0] datacount=2 progbufsize=8 Info : Examined RISC-V core; found 1 harts Info : hart 0: XLEN=32, misa=0x40901125 [riscv.cpu.0] Target successfully examined. Info : starting gdb server for riscv.cpu.0 on 3333 Info : Listening on port 3333 for gdb connections Info : device id = 0xe339e339 Info : flash size = 58169kbytes erased sectors 0 through 58168 on flash bank 0 in 0.195708s 11:25:03:512 >> Starting to Download... "/home/lth/MounRiver_Studio_Community_Linux_x64_V110/MRS_Community/toolchain/OpenOCD/bin/openocd" -f "/home/lth/MounRiver_Studio_Community_Linux_x64_V110/MRS_Community/toolchain/OpenOCD/bin/wch-riscv.cfg" -c init -c halt -c "program \"/home/lth/src/CH32V307V-EVT-R1/first/obj/first.hex\"" -c exit Open On-Chip Debugger 0.11.0+dev-02215-gcc0ecfb6d-dirty (2022-03-30-18:53) Licensed under GNU GPL v2 For bug reports, read http://openocd.org/doc/doxygen/bugs.html Info : only one transport option; autoselect 'jtag' Ready for Remote Connections Info : WCH-Link version 2.3 Info : wlink_init ok Info : This adapter doesn't support configurable speed Info : JTAG tap: riscv.cpu tap/device found: 0x00000001 (mfg: 0x000 (<invalid>), part: 0x0000, ver: 0x0) Warn : Bypassing JTAG setup events due to errors Info : [riscv.cpu.0] datacount=2 progbufsize=8 Info : Examined RISC-V core; found 1 harts Info : hart 0: XLEN=32, misa=0x40901125 [riscv.cpu.0] Target successfully examined. Info : starting gdb server for riscv.cpu.0 on 3333 Info : Listening on port 3333 for gdb connections Info : JTAG tap: riscv.cpu tap/device found: 0x00000001 (mfg: 0x000 (<invalid>), part: 0x0000, ver: 0x0) Warn : Bypassing JTAG setup events due to errors ** Programming Started ** Info : device id = 0x263e6d6e Info : flash size = 256kbytes ** Programming Finished ** 11:25:06:504 >> Starting to Verify... "/home/lth/MounRiver_Studio_Community_Linux_x64_V110/MRS_Community/toolchain/OpenOCD/bin/openocd" -f "/home/lth/MounRiver_Studio_Community_Linux_x64_V110/MRS_Community/toolchain/OpenOCD/bin/wch-riscv.cfg" -c init -c halt -c "verify_image \"/home/lth/src/CH32V307V-EVT-R1/first/obj/first.hex\"" -c exit Open On-Chip Debugger 0.11.0+dev-02215-gcc0ecfb6d-dirty (2022-03-30-18:53) Licensed under GNU GPL v2 For bug reports, read http://openocd.org/doc/doxygen/bugs.html Info : only one transport option; autoselect 'jtag' Ready for Remote Connections Info : WCH-Link version 2.3 Info : wlink_init ok Info : This adapter doesn't support configurable speed Info : JTAG tap: riscv.cpu tap/device found: 0x00000001 (mfg: 0x000 (<invalid>), part: 0x0000, ver: 0x0) Warn : Bypassing JTAG setup events due to errors Info : [riscv.cpu.0] datacount=2 progbufsize=8 Info : Examined RISC-V core; found 1 harts Info : hart 0: XLEN=32, misa=0x40901125 [riscv.cpu.0] Target successfully examined. Info : starting gdb server for riscv.cpu.0 on 3333 Info : Listening on port 3333 for gdb connections Info : Verify Success 11:25:08:306 >> Starting to Reset... "/home/lth/MounRiver_Studio_Community_Linux_x64_V110/MRS_Community/toolchain/OpenOCD/bin/openocd" -f "/home/lth/MounRiver_Studio_Community_Linux_x64_V110/MRS_Community/toolchain/OpenOCD/bin/wch-riscv.cfg" -c init -c wlink_reset_resume -c exit Open On-Chip Debugger 0.11.0+dev-02215-gcc0ecfb6d-dirty (2022-03-30-18:53) Licensed under GNU GPL v2 For bug reports, read http://openocd.org/doc/doxygen/bugs.html Info : only one transport option; autoselect 'jtag' Ready for Remote Connections Info : WCH-Link version 2.3 Info : wlink_init ok Info : This adapter doesn't support configurable speed Info : JTAG tap: riscv.cpu tap/device found: 0x00000001 (mfg: 0x000 (<invalid>), part: 0x0000, ver: 0x0) Warn : Bypassing JTAG setup events due to errors Info : [riscv.cpu.0] datacount=2 progbufsize=8 Info : Examined RISC-V core; found 1 harts Info : hart 0: XLEN=32, misa=0x40901125 [riscv.cpu.0] Target successfully examined. Info : starting gdb server for riscv.cpu.0 on 3333 Info : Listening on port 3333 for gdb connections ------------------------------End ------------------------------ Operation Finished (took 6s.176ms)

Serial console

In a console window a serial monitor can be run which will produce the following output:

lth@ncpws04:~/openwrt-bpir2$ microcom -f -s 115200 -p /dev/ttyACM0 connected to /dev/ttyACM0 Escape character: Ctrl-\ Type the escape character to get to the prompt. SystemClk:72000000 This is printf example

Notice that the output will actually be printed twice (not shown above) because the MCU is reset twice during the flashing process.

Single step debugging

To be added

Getting Started

SysTick Timer

Coming from STM32, I like to have a counter running calibrated at ms resolution (HAL_GetTick() on STM32). By default that is not available on the CH32V307 using the provided SDK. Fortunately it is quite easy to implement:

/*

* systick.c

*

* Created on: Jun 29, 2022

* Author: lth

*/

//#include "ch32v30x.h"

#include "systick.h"

uint32_t uwTick = 0;

/*********************************************************************

* @fn SysTick_Handler

*

* @brief This function handles SysTick interrupt.

*

* @return none

*/

__attribute__((interrupt("WCH-Interrupt-fast"))) void SysTick_Handler(void) {

SysTick->SR=0;

++uwTick;

}

/*********************************************************************

* @fn Systick_Init

*

* @brief Initializes Systick.

*

* @return none

*/

void Systick_Init(void) {

/*Configuration interrupt priority*/

NVIC_InitTypeDef NVIC_InitStructure = {0};

NVIC_InitStructure.NVIC_IRQChannel = SysTicK_IRQn;

NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 0;//Seeing priority

NVIC_InitStructure.NVIC_IRQChannelSubPriority = 0;//Response priority

NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE;//Enable

NVIC_Init(&NVIC_InitStructure);

/*Configuration timer*/

SysTick->CTLR= 0;

SysTick->SR = 0;

SysTick->CNT = 0;

SysTick->CMP = SystemCoreClock / 1000; //The latter 1000 represents 1000Hz (that is, 1MS to interrupt once)

SysTick->CTLR= 0xf;

}

*********************************************************************

* @fn GetTick

*

* @brief Get current tick in ms resolution

*

* @return Current tick

*/

uint32_t GetTick() {

return uwTick;

}

Call the Systick_Init() at the beginning of main and GetTick() will return the number of milliseconds since startup (with wraparound after about 1 1/2 month).

GPIOs

To be added