Difference between revisions of "STM32 Watchdogs"

| Line 8: | Line 8: | ||

[[File:watchdog.gif|400px]] | [[File:watchdog.gif|400px]] | ||

| − | In the [[STM32]], the [[IWDG]] is built-into the [[MCU]] itself. | + | In the [[STM32]], the [[IWDG]] is built-into the [[MCU]] itself, but it is still a completely independent device. So much in fact that it is not possible to read the counter value during run-time. |

| + | |||

| + | === Calculating Time === | ||

| + | |||

| + | The [[IWDG]] is clocked from the internal (or external) low speed timer. By default, without an external crystal, this is running at 32000 kHz. The formula to calculate the reset time is like this: | ||

| + | |||

| + | [[File:IWDG Formula.png|600px]] | ||

== Window Watchdog (WWDG) == | == Window Watchdog (WWDG) == | ||

Revision as of 02:28, 4 November 2024

From the point of view of embedded systems, a watchdog is a device which monitors a system and is able to restart the system if or when something goes wrong. STM32 MCUs are equipped with two watchdogs: the Independent Watchdog (IWDG) and a Window Watchdog (WWDG). These watchdogs will be described in the following sections.

Independent Watchdog (IWDG)

The IWDG is, as the name implies, an independent device which watches over the MCU. It can be illustrated like this:

In the STM32, the IWDG is built-into the MCU itself, but it is still a completely independent device. So much in fact that it is not possible to read the counter value during run-time.

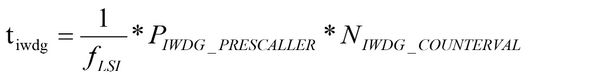

Calculating Time

The IWDG is clocked from the internal (or external) low speed timer. By default, without an external crystal, this is running at 32000 kHz. The formula to calculate the reset time is like this:

Window Watchdog (WWDG)

To be added

Miscellaneous Links

To be added