Difference between revisions of "Core Coupled Memory"

Jump to navigation

Jump to search

| (One intermediate revision by the same user not shown) | |||

| Line 3: | Line 3: | ||

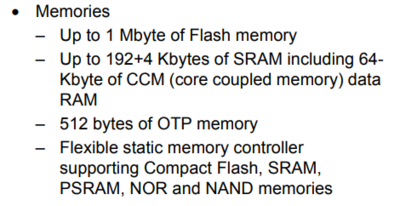

According to the [https://www.st.com/resource/en/datasheet/dm00037051.pdf datasheet], the memory in [[STM32F405]] is: | According to the [https://www.st.com/resource/en/datasheet/dm00037051.pdf datasheet], the memory in [[STM32F405]] is: | ||

| + | <div class="res-img"> | ||

[[File:STM32F405 Memory.png|400px]] | [[File:STM32F405 Memory.png|400px]] | ||

| + | </div> | ||

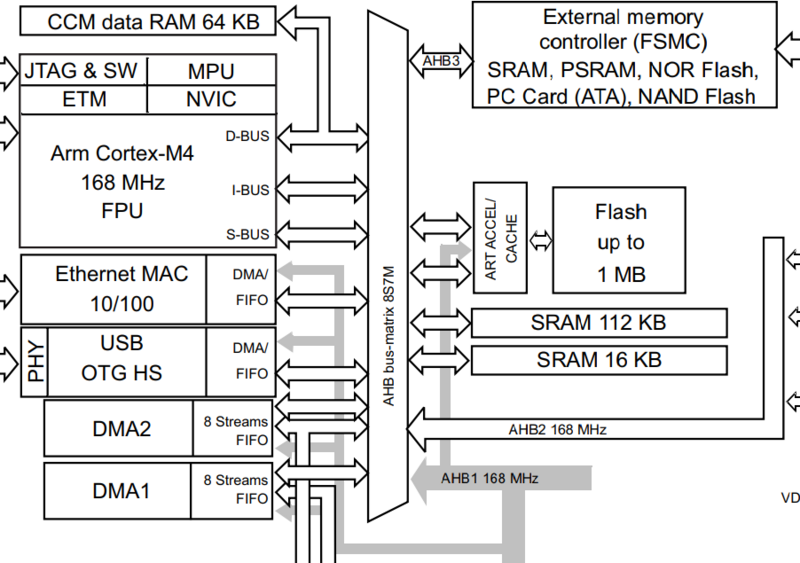

In the block diagram it is shown like this: | In the block diagram it is shown like this: | ||

| − | [[File:STM32F405 Memory Architecture.png| | + | <div class="res-img"> |

| + | [[File:STM32F405 Memory Architecture.png|800px]] | ||

| + | </div> | ||

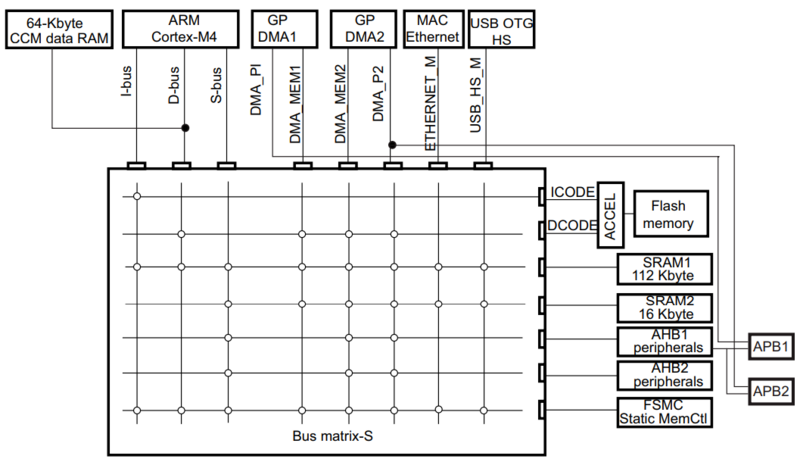

It is worth noticing a few things. As the name implies this RAM is connected directly to the [[MCU]] core but separate from the AHB bus matrix. Looking at the bus matrix: | It is worth noticing a few things. As the name implies this RAM is connected directly to the [[MCU]] core but separate from the AHB bus matrix. Looking at the bus matrix: | ||

| − | [[File:STM32F405 Bus Matrix.png| | + | <div class="res-img"> |

| + | [[File:STM32F405 Bus Matrix.png|800px]] | ||

| + | </div> | ||

| + | |||

| + | == Usage Examples == | ||

| + | |||

| + | * [[STM32 FreeRTOS|Using CCMRAM for FreeRTOS Heap]] | ||

Latest revision as of 01:22, 2 November 2024

Some STM32 MCUs include a feature called CCMRAM (Core Coupled Memory), which is separate from the regular SRAM region.

According to the datasheet, the memory in STM32F405 is:

In the block diagram it is shown like this:

It is worth noticing a few things. As the name implies this RAM is connected directly to the MCU core but separate from the AHB bus matrix. Looking at the bus matrix: